Current Project (2018-2025)

Research Team: Lieuwe Leene, Peilong Feng, Andrea Mifsud, Timothy Constandinou

Collaborators: Themis Prodromakis (Edinburgh), Christos Papavassilliou (CAS Group, EEE) and Dirk Koch, Piotr Dudek (Manchester)

Funding: EPSRC Programme Grant EP/R024642/1

Our vision is to rejuvenate modern electronics by developing and enabling a new approach to electronic systems where reconfigurability, scalability, operational flexibility/resilience, power efficiency and cost-effectiveness are combined. This vision will be delivered by breaking out of the large, but comprehensively explored realm of CMOS technology upon which virtually all modern electronics are based; consumer and non-consumer alike.

Introducing novel nanoelectronic components never before used in the technology we all carry around in our phones will introduce new capabilities that have thus far been unattainable due to the limitations of current hardware technology. The resulting improved capability of engineers to squeeze more computational power in ever smaller areas at ever lower power costs will unlock possibilities such as: a) truly pervasive Internet-of-Things computing where minute sensors consuming nearly zero power monitor the world around us and inform our choices, b) truly smart implants that within extremely limited power and size budgets can not only interface with the brain, but also process that data in a meaningful way and send the results either onwards to e.g. a doctor, or even feed it back into the brain for further processing, c) radiation-resistant electronics to be deployed in satellites and aeroplanes, civilian and military and improve communication reliability while driving down maintenance costs.

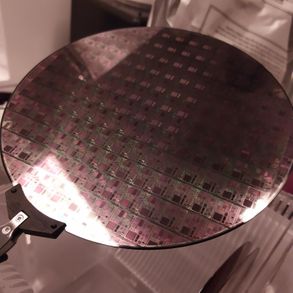

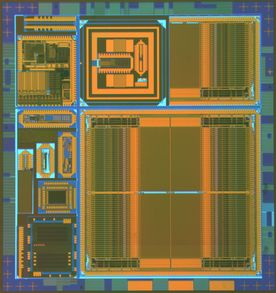

Engineering Runs

Publications

2024

- A. Mifsud, A. Malik, A. Alshaya, P. Feng, and T. G. Constandinou, “A closed-loop readout circuit with voltage drop mitigation for emerging resistive technologies,” in IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1–4, 2024.

2023

- A. Mifsud and T. G. Constandinou, “Towards a CMOS-process-portable ReRAM PDK,” in 21st IEEE Interregional NEWCAS Conference, 2023. doi: https://doi.org/10.1109/NEWCAS57931.2023.10198171

2022

- A. Mifsud, J. Shen, P. Feng, L. Xie, C. Wang, Y. Pan, S. Maheshwari, S. Agwa, S. Stathopoulos, S. Wang, A. Serb, C. Papavassiliou, T. Prodromakis, and T. G. Constandinou, “A CMOS-based characterisation platform for emerging RRAM technologies,” in IEEE International Symposium on Circuits and Systems (ISCAS), 2022. doi: https://doi.org/10.1109/ISCAS48785.2022.9937343

- D. Antoniades, P. Feng, A. Mifsud, and T. G. Constandinou, “An open-source RRAM compiler,” in 2022 20th IEEE Inter-regional NEWCAS Conference (NEWCAS), 2022. doi: https://doi.org/10.1109/NEWCAS52662.2022.9842222

2021

- S. Maheshwari, S. Stathopoulos, J. Wang, A. Serb, Y. Pan, A. Mifsud, L. B. Leene, J. Shen, C. Papavassiliou, T. G. Constandinou, and T. Prodromakis, “Design flow for hybrid CMOS/memristor systems–part I: Modeling and verification steps,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 12, pp. 4862–4875, 2021. doi: https://doi.org/10.1109/TCSI.2021.3122343

- S. Maheshwari, S. Stathopoulos, J. Wang, A. Serb, Y. Pan, A. Mifsud, L. B. Leene, J. Shen, C. Papavassiliou, T. G. Constandinou, and T. Prodromakis, “Design flow for hybrid CMOS/memristor systems–part II: Circuit schematics and layout,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 12, pp. 4876–4888, 2021. doi: https://doi.org/10.1109/TCSI.2021.3122381